Cours Architecture des ordinateurs en PDF (Avancé)

Architecture des ordinateurs : Définition : l'architecture des ordinateurs étudie l'organisation des composants matériels et leur coopération fonctionnelle — du niveau transistor jusqu'à l'ISA et la gestion des mémoires et interruptions. Sujet central en informatique matérielle et logicielle, il permet de comprendre les performances, la consommation et la correction des systèmes numériques dans des contextes tels que l'embarqué, l'architecture microprocesseur et l'optimisation logicielle. Ce support PDF gratuit inclut des sujets de travaux pratiques corrigés et des fiches de référence téléchargeables.

🎯 Ce que vous allez apprendre

- Codages et arithmétique binaire — maîtrise des représentations (binaire, hexadécimal) et des codages signés (complément à deux, complément vrai). Étude des formats flottants et fixe : diagnostic des erreurs d'overflow, conception d'ALU et interprétation des résultats machine ; conversion, détection de débordements et choix d'un format numérique adapté à un algorithme. Additionneur complet : principe de fonctionnement bit-à-bit avec propagation de la retenue, comparaison des architectures ripple-carry et carry‑lookahead pour réduire la latence dans des additionneurs multi-bit.

- Logique physique et combinatoire — étude des niveaux logiques, des transistors CMOS et de la synthèse des portes (NAND, NOR). Analyse du temps de propagation et du chemin critique : estimer la latence d'un circuit, proposer simplifications logiques et vérifier la robustesse temporelle. Termes et composants clés abordés : circuits combinatoires, multiplexeur, démultiplexeur, logique d'arbitrage et conversion de niveaux pour l'intégration dans un microprocesseur.

- Logique séquentielle et chemin de données — conception des verrous/bascule (RS, D), registres, mémoire RAM et séquencement du chemin de données d'un microprocesseur. Structuration d'un datapath synchronisé et implémentation d'un contrôleur : définition des registres nécessaires, conception d'un séquenceur et vérification de la cohérence des fronts d'horloge.

- Couche ISA et micro-instructions — codage des instructions en mémoire, fetch, et génération de micro-instructions via machines à états finis ou microprogramme. Comprendre comment l'ISA mappe sur un datapath est crucial pour l'optimisation compilateur-architecture; analyse du format d'instruction, simulation du fetch et description du micro‑séquencement d'instructions.

- Pile, procédures et conventions d'appel — rôle du pointeur de pile pour passer arguments, sauvegarder contextes et exécuter retours de routines. Tracer une pile d'exécution, expliquer l'impact des appels récursifs et concevoir conventions d'appel simples pour optimiser l'utilisation des registres et minimiser les coûts de sauvegarde.

- Mémoire, cache et cohérence — panorama des mémoires (ROM, RAM, masse), hiérarchie mémoire, caches (direct-mapped, associatif, n-ways) et problèmes de cohérence mémoire. Estimer les effets de localité, choisir une organisation de cache et expliquer les enjeux de cohérence entre caches et mémoire centrale; comparaison des politiques write-back et write-through et impact sur performances et latence.

Fonctionnement de l'Unité Centrale et du CPU

L'unité centrale orchestre les phases fetch‑decode‑execute, gère les transferts vers et depuis la hiérarchie mémoire et déclenche les traitements d'interruption lors des E/S. Le couplage entre le contrôleur, l'ALU et les registres conditionne la latence d'exécution et la capacité à maintenir l'atomicité des opérations mémoire, en particulier en présence de caches multi‑niveaux et d'unités d'exécution out‑of‑order. Comprendre ces interactions permet d'analyser les gains d'optimisations compilateur-architecture et de concevoir des mécanismes d'ordonnancement et de cohérence adaptés aux contraintes applicatives.

Organisation de l'Unité Centrale (CPU)

L'organisation interne sépare clairement les fonctions : l'ALU effectue les opérations arithmétiques et logiques, les registres fournissent des opérandes rapides et l'unité de contrôle séquence les micro‑opérations. Les chemins de données (buses internes) permettent les transferts entre registres, mémoire cache et unités fonctionnelles. Les interruptions et la logique de gestion des exceptions sont intégrées à l'unité de contrôle afin d'assurer un retour d'état cohérent lors d'interactions avec les périphériques.

Composants matériels : Processeur, Mémoire et Bus

Les composants matériels centraux comprennent le processeur (unités d'exécution, pipeline, buffers), la mémoire (caches, RAM, ROM) et les bus de communication qui relient ces éléments. Le dimensionnement du bus, la largeur des mots et la politique d'accès influencent la bande passante et la latence perçue par le système, tandis que les mécanismes de synchronisation et d'arbitrage conditionnent la coexistence de plusieurs masters (DMA, CPU, périphériques). La compréhension de ces composants facilite l'évaluation des compromis entre performance, consommation et complexité de la microarchitecture.

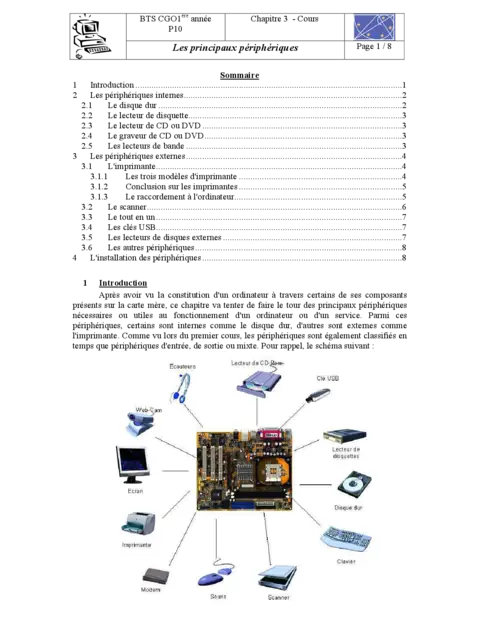

Architecture matérielle et périphériques d'entrée-sortie

La communication entre l'unité centrale et les composants de base s'effectue via le bus système et des mécanismes d'E/S dédiés. Le processeur adresse des ports ou des régions mémoire réservées (memory-mapped I/O) pour piloter périphériques et contrôleurs, tandis que des contrôleurs DMA prennent en charge des transferts de données volumineux sans surcharger le CPU. Les politiques d'accès, les temps de latence du bus de données et les priorités d'interruption influencent directement la qualité de service pour les périphériques d'entrée‑sortie et doivent être intégrées dès la phase de microarchitecture.

- Clavier

- Écran

- Souris

- Unité centrale (boîtier/CPU) et contrôleurs associés

Analyse des circuits combinatoires et séquentiels

L'analyse des circuits combinatoires porte sur la logique fonctionnelle sans mémoire (portes, multiplexeurs, démultiplexeurs, additionneurs) et leur caractérisation temporelle. La conception séquentielle ajoute des éléments d'état (bascule, registres) et exige une vérification des contraintes de timing pour assurer la stabilité du chemin de données. Ce chapitre met en relation le système binaire, les circuits combinatoires et la structure du microprocesseur pour permettre la synthèse, la simulation et la validation de modules réutilisables dans une architecture de type pipeline ou monobloc.

Architecture de Von Neumann vs Harvard

La distinction Von Neumann / Harvard concerne la séparation (ou non) des buses pour instructions et données. Dans l'architecture Von Neumann, instructions et données partagent la même mémoire et le même bus, ce qui simplifie le design mais peut créer des goulots d'étranglement (von Neumann bottleneck). L'architecture Harvard utilise des chemins séparés, réduisant les conflits et permettant des accès simultanés, au prix d'une complexité matérielle accrue. Le choix dépend des objectifs de débit, de latence et des contraintes d'intégration dans le microprocesseur.

Applications pratiques de l'architecture

La cartographie ISA→microarchitecture a des impacts visibles sur les processeurs modernes (x86, ARM) : gestion du pipeline, prédiction de branchement, spéculation et politiques de cache influent sur le throughput et la consommation énergétique. L'analyse de cas concrets montre comment un format d'instruction ou un choix de pipeline favorise certaines classes d'algorithmes (parallélisme SIMD, calcul entropique, accès mémoire intensif). Ces applications relient principes théoriques, mesures de performance et options d'optimisation au niveau du compilateur ou du système d'exploitation.

📑 Sommaire du document

Le document est structuré pour progresser du fondamental vers la microarchitecture : codages et circuits, logique séquentielle, ISA et interactions matérielles, puis études de cas et exercices corrigés. Chaque chapitre inclut définitions, illustrations de montage et exercices pratiques avec solutions pour faciliter la mise en application.

- Codages et opérations binaires

- Couche physique et couche logique

- Couche ISA

- Procédures, pile et pointeur de pile

- Traduction, Compilation, interprétation

- Mémoire

- Périphériques et leur gestion par interruption

- Carte de référence

💡 Pourquoi choisir ce cours ?

Rédigé par Jeremy Fix, ce support couvre l'ensemble de la chaîne : des transistors CMOS et portes logiques jusqu'à l'ISA, la traduction et la gestion des périphériques. Le document combine exposés théoriques et exercices pratiques : les sujets de travaux pratiques sont corrigés et incluent des solutions détaillées pour faciliter la vérification et l'auto‑évaluation. La présence d'une carte de référence et d'une bibliographie rend l'usage opérationnel pour la préparation d'examens ou l'intégration en projet matériel/logiciel.

Exercices d'architecture des ordinateurs avec corrigés

Les séries d'exercices proposent des cas pratiques sous Logisim, des problèmes d'arithmétique binaire, des schémas de datapath à compléter et des études de séquencement. Chaque exercice est accompagné d'un corrigé expliquant le principe de fonctionnement, les choix d'implémentation et les critères de validation, afin de renforcer la compréhension conceptuelle et l'aptitude à diagnostiquer des erreurs matérielles ou logicielles.

👤 À qui s'adresse ce cours ?

- Public cible : étudiants en informatique ou ingénierie électronique, développeurs systèmes et toute personne intervenant sur la conception matérielle ou l'optimisation bas‑niveau souhaitant relier logique numérique, ISA et gestion mémoire.

- Prérequis : maîtrise des systèmes de numération (binaire/hexadécimal), notions d'algèbre booléenne et logique combinatoire/séquentielle, ainsi que des connaissances de base en programmation et en structures de données.

❓ Foire Aux Questions (FAQ)

Comment le complément à deux gère-t-il les entiers négatifs et les dépassements arithmétiques ? Le complément à deux représente les entiers relatifs en utilisant un bit de signe implicite et permet d'effectuer additions/subtractions sans traitement spécial du signe; l'overflow se détecte via la discordance entre le bit de signe des opérandes et du résultat, méthode utilisée couramment pour simplifier la conception d'une ALU.

Que couvre la section sur cohérence de cache et mémoire centrale ? Le chapitre identifie les anomalies entre caches et mémoire centrale liées aux opérations concurrentes et décrit les stratégies générales de maintien de cohérence (invalidation ou mise à jour écriture), ainsi que l'impact des politiques write-back versus write-through sur performances et latence. La gestion des périphériques d'entrée/sortie par interruption illustre les mécanismes d'E/S asynchrones et leur interaction avec la mémoire.