Cours Circuits et architecture des ordinateurs en PDF (M1)

Circuits et architecture des ordinateurs : éléments essentiels. Discipline qui étudie la représentation de l'information en bits, la conception des circuits logiques et séquentiels et l'organisation matérielle des micro‑processeurs selon le modèle de von Neumann. Ce support universitaire détaille les codages (entiers, IEEE 754, BCD), les structures arithmétiques (additionneurs, indicateurs) et les composants mémoires, ainsi que la description et la programmation du processeur pédagogique LC-3.

🎯 Ce que vous allez apprendre

- Représentations des données — étude précise des codages binaires : entiers non signés, représentation en complément à deux, représentation biaisée pour exposants et normes flottantes IEEE 754. Vous comprendrez pourquoi chaque format est choisi selon contraintes d'opération (test de signe, extension signée/non signée) et sa conséquence sur le calcul des indicateurs et le traitement matériel des données.

- Conception des additionneurs et circuits arithmétiques — comparaison et analyse de topologies : semi‑additionneur, additionneur complet, ripple‑carry, carry‑lookahead, additionneur récursif et hybrides. La fiche explique l'impact des retenues (carry), des délais logiques et des indicateurs (overflow, retenue de poids fort) sur le débit et la latence des unités ALU, et fournit des critères de choix et de dimensionnement selon contraintes temps/coût.

- Mémoires et bascules — inventaire des mémoires statiques et dynamiques, bascules RS et D, structures simples (mémoire 4 × 3 bits) et notions de timing. L'étudiant distinguera SRAM/DRAM, comprendra l'usage des bascules pour l'enregistrement d'état et concevra des éléments de stockage adaptés à une unité de traitement.

- Circuits séquentiels et architecture d'un micro‑processeur — principes des automates finis, construction d'une chaîne séquentielle, et découpage en unité de contrôle, unité de traitement et mémoire. Un circuit séquentiel est un circuit dont les sorties dépendent des entrées actuelles mais aussi des états antérieurs. Vous serez capable de modéliser un chemin de données, définir l'interaction contrôle/données et analyser les besoins en synchronisation et horloge.

- Description et programmation du processeur LC-3 — registres, organisation mémoire, jeu d'instructions et chemins de données du

LC-3, complétés par exercices de programmation en assembleur (appels de sous‑programmes, pile, sauvegarde des registres). Le document inclut des TD pratiques utilisant le logiciel de simulation logique TKGate (v1.8.7) pour relier schéma logique et exécution réelle. - Pipeline et gestion de la mémoire — principes de pipeline : découpage en étages, réalisation matérielle et aléas (hazards). Le cours aborde aussi mémoires associatives, caches et mémoire virtuelle, permettant d'analyser compromis latence/bande passante et stratégies d'atténuation des conflits mémoire.

Définition de l'architecture des ordinateurs

L'architecture des ordinateurs concerne l'organisation et l'interaction des composants matériels et logiques qui exécutent les programmes. Elle définit les structures de données matérielles, les chemins de données et les mécanismes de contrôle : unité de commande, unité arithmétique et logique, registres et hiérarchie mémoire. Cette description permet de relier le schéma logique à l'exécution des instructions et à la performance globale du système.

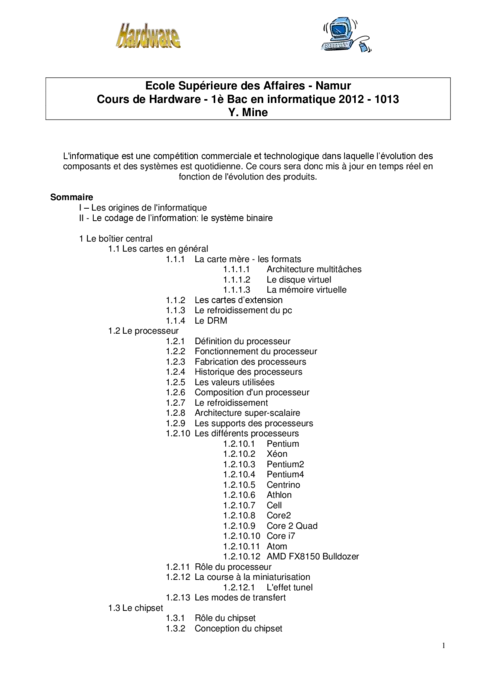

Les composants matériels

- Écran (affichage)

- Clavier (interface utilisateur)

- Unité centrale (traitement et contrôle)

- Mémoire (stockage volatil et non‑volatile)

Composants et fonctionnement de l'unité centrale

L'unité centrale (UC) coordonne l'exécution des instructions et le contrôle des périphériques. Elle interprète le code machine, orchestre les transferts entre registres et mémoire, et pilote l'unité arithmétique/logique pour effectuer les opérations. Le contrôle temporel (horloge) et les signaux de contrôle synchronisent lectures, écritures et accès DMA. L'UC assure aussi la gestion des interruptions et la communication avec les périphériques via des contrôleurs dédiés, ce qui conditionne la réactivité et le débit du système.

Différences entre architectures CISC et RISC

Les architectures CISC privilégient un jeu d'instructions riche, parfois plus complexes à décoder mais pouvant réduire le nombre d'instructions par programme. Les architectures RISC proposent un jeu réduit, instructions simples et pipeline-friendly, favorisant l'exécution à haut débit et la simplicité du schéma logique. Le choix entre CISC et RISC influe sur la conception du pipeline, la taille des instructions, la gestion des modes d'adressage et les stratégies d'optimisation du compilateur.

📑 Sommaire du document

- Circuits et architecture des ordinateurs en M1

- Historique

- Représentation des données

- Additionneurs

- Mémoire

- Circuits séquentiels et architecture générale d’un micro‑processeur

- Description du LC-3

- Programmation en assembleur du LC-3

💡 Pourquoi choisir ce cours ?

Support de cours universitaire d'Olivier Carton (Université Paris Diderot) structuré pour un public M1, liant théorie des codages et conception matérielle jusqu'à l'assembleur pédagogique LC-3. L'approche est progressive : des portes logiques et tables de Karnaugh aux chemins de données et au pipeline, avec TD pratiques utilisant le logiciel de simulation logique TKGate (v1.8.7) et exercices d'assembleur pour renforcer la mise en pratique. Le document se distingue par sa couverture du flux informationnel — du bit au processeur — et par l'intégration d'exemples concrets et d'études comparatives d'architectures.

👤 À qui s'adresse ce cours ?

- Public cible : étudiants en master informatique/ingénierie, ingénieurs systèmes embarqués ou développeurs bas‑niveau cherchant une compréhension approfondie des circuits numériques et de la micro‑architecture.

- Prérequis : maîtrise de la logique booléenne et des opérations binaires, connaissances en arithmétique binaire (complément à deux), notions de programmation impérative (C ou équivalent) et bases d'électronique numérique (portes logiques, bascules).

❓ Foire Aux Questions (FAQ)

Comment la représentation en complément à deux simplifie‑t‑elle l'addition matérielle ?

En complément à deux, l'addition signée s'obtient par la même addition binaire que pour les entiers non signés : le circuit n'a pas besoin de chemins séparés pour signes opposés. Le document montre également comment détecter l'overflow via la relation entre la retenue d'entrée et la retenue de sortie du bit de signe (détection par C_k-1 ⊕ C_k), facilitant l'implémentation matérielle des indicateurs.

Quels aléas du pipeline sont traités et quelles protections sont évoquées ?

Le document distingue aléas structurels, de données et de contrôle, et décrit leurs implications pour les étages du pipeline. Les remèdes techniques présentés incluent l'insertion de stalls (bulles), le forwarding/bypass pour réduire les latences de données, ainsi que des mécanismes de contrôle pour limiter les interruptions du flux d'instructions.