Cours Initiation au Langage Machine en PDF (Intermédiaire)

Initiation au Langage Machine : Ce qu'il faut savoir. Le langage machine, ou code machine, est la représentation binaire des instructions exécutées par un processeur ; dans ce support de cours universitaire le document définit un microprocesseur simplifié MP0 et son langage LM0 pour illustrer ces concepts de base. Comprendre l'encodage des instructions, les modes d'adressage et le jeu de registres est fondamental pour saisir le fonctionnement des machines et optimiser du code bas niveau dans des contextes embarqués ou d'architecture.

🎯 Apprendre l'Assembleur et le Langage Machine

- Architecture du processeur MP0 — identification des composants essentiels (

CO,SR,D0/D1,A0/A1,PP) et de leurs rôles dans l'exécution d'un programme ; l'étudiant pourra localiser le flux d'exécution et expliquer comment les registres et le compteur ordinal interagissent pour piloter les instructions sur ce microprocesseur pédagogique. - Modes d'adressage (immédiat, direct, indirect) — description précise des trois modes et de leurs syntaxes symboliques, avec exemples concrets ; l'apprenant saura choisir le mode adapté selon la contrainte d'accès mémoire et transcrire des accès mémoire en instructions LM0.

- Format et encodage des instructions LM0 — structure sur 2 octets (octet d'opcode et octet de valeur/opérande), règles quand le second octet vaut 0 ; résultat : capacité à lire et écrire des séquences d'octets correspondant à des instructions et à interpréter l'encodage binaire.

- Jeu d'instructions et effets sur le registre d'état SR — transfert (

MOVE,PSH,POP), arithmétique (ADD,SUB,MUL,DIV) et logique (NOT,AND,OR) ainsi que instructions de saut ; l'étudiant comprendra l'impact de chaque opération sur les bitsZetNduSRet saura prédire les conséquences d'une séquence d'instructions. - Gestion de la pile et conventions (

PP,PSH,POP) — fonctionnement LIFO, initialisation du pointeurPPà 255 et traduction desPSH/POPen séquencesMOVE/ADD/SUB; capacité à concevoir des routines d'appel/retour simples et à gérer correctement le flux de données sur la pile.

Architecture des ordinateurs et processeur MP0

Ce cours s'inscrit dans un cursus d'Architecture des ordinateurs en apportant un module concret et opérationnel centré sur un microprocesseur pédagogique, MP0. Les concepts exposés — jeu de registres, chemin de données, unité de contrôle et mémoire — correspondent aux thèmes couramment enseignés en première année d'architecture ou en filière systèmes embarqués. Des exercices de lecture d'encodage, d'optimisation de séquences et de simulation du pipeline renforcent la compréhension des interactions matérielles sous-jacentes.

La présentation de MP0 en tant que microprocesseur réduit permet d'isoler les effets de chaque instruction sans les complications d'une architecture commerciale complète. Au niveau du microprocesseur, la manipulation des bits et des octets (masquage, décalage, tests de drapeaux) est présentée explicitement pour montrer comment les opérations binaires influent sur le flux de données et le registre d'état.

Cette approche facilite la transition vers des modèles plus complexes et prépare à des sujets avancés : conception de jeux d'instructions, microarchitecture et contraintes temporelles en temps réel.

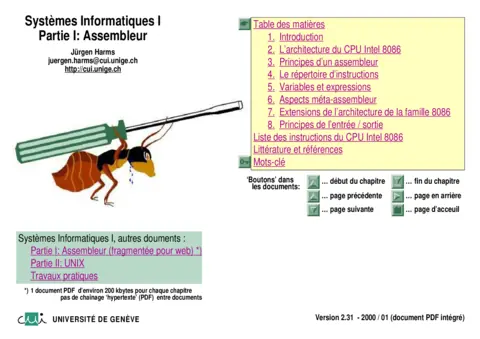

Lien entre Langage Machine et Assembleur

Le document établit un pont pratique entre le code machine binaire et son pendant symbolique, l'assembleur. En travaillant sur LM0, l'apprenant constate comment une instruction machine se traduit en mnémonique, comment les opérandes sont représentés et comment les directives d'assembleur simplifient l'écriture et la maintenance du code bas niveau. Ce lien facilite la rédaction d'assembleur lisible et la compréhension des optimisations locales à appliquer lors de la programmation bas niveau.

Des exemples comparatifs montrent la correspondance entre séquences en assembleur et séquences d'octets, ce qui aide à diagnostiquer des erreurs d'encodage, à comprendre les conventions d'appel et à interpréter des dump mémoire lors de sessions de débogage matériel ou d'émulation logicielle.

Processus de compilation/assemblage : pour un langage compilé comme le C, le compilateur traduit le code source en code assembleur ensuite converti en code machine par l'assembleur et le linker ; le binaire final contient les séquences d'octets exécutables par le processeur. Pour des langages interprétés tels que Python, l'exécution standard produit un bytecode interprété par une machine virtuelle, mais des outils (Cython, compilateurs natifs) peuvent générer du code C compilable, puis de l'assembleur et enfin du code machine.

Du langage C au code machine : le rôle de l'assembleur

Le passage de C au binaire passe par plusieurs étapes : analyse syntaxique du source, génération d'une représentation intermédiaire, puis production d'assembleur ciblé sur l'architecture. L'assembleur traduit les mnémoniques et directives en opcodes et opérandes binaires conformes au format du microprocesseur. Comprendre cette chaîne permet d'optimiser le code C en guidant le compilateur via des contraintes, des intrinsics ou des sections d'assembleur inline, et d'expliquer les choix de conventions d'appel et d'alignement mémoire observés dans le binaire.

Structure binaire des instructions du microprocesseur

Chaque instruction LM0 occupe deux octets : l'octet d'opcode spécifie l'opération et ses variantes, l'octet d'opérande transporte une valeur immédiate ou un index d'adresse. Cette taille fixe simplifie le décodage matériel et la mise en œuvre d'un pipeline pédagogique. La structure binaire est présentée bit à bit pour les principaux opcodes, avec tableaux d'encodage et exemples d'interprétation binaire pour faciliter la lecture d'un dump mémoire.

💡 Pourquoi choisir ce cours ?

La méthode privilégie un microprocesseur "jouet" (MP0) et un langage LM0 minimaliste pour mettre en lumière les mécanismes fondamentaux sans la complexité d'un jeu d'instructions industriel. Support de cours universitaire (UMR 7030, Université Paris 13) : les explications s'appuient on des exemples chiffrés et des séquences d'instructions, favorisant la mise en pratique et la vérifiabilité des résultats. La comparaison explicite entre LM0 et C facilite l'apprentissage de la programmation bas niveau pour les développeurs systèmes et embarqués.

Public cible et objectifs

- Public cible : étudiants en architecture des ordinateurs, développeurs systèmes ou embarqués débutant en assembleur et souhaitant comprendre le lien concret entre instructions machine et comportements matériels.

- Prérequis : notions d'arithmétique binaire et octets, familiarité avec la programmation impérative (par exemple C) et compréhension basique de la mémoire (adresse, pointeur).

❓ Foire Aux Questions (FAQ)

Question : Comment est codée une instruction LM0 et quel rôle joue le second octet ? Le format LM0 utilise deux octets par instruction : le premier encode l'opération et le type d'opérande, le second transporte une valeur immédiate ou l'indice d'adresse lorsque requis. Le second octet permet un décodage uniforme et simplifie la mise en œuvre d'un pipeline pédagogique en remplaçant des formats variables par une taille fixe ; il représente directement les octets du code machine présents en mémoire.

Question : En adresse indirecte, comment MP0 accède-t-il à la donnée pointée par un registre d'adresse ? L'Adressage indirect utilise un registre d'adresse (A0 ou A1) contenant l'adresse mémoire cible ; une instruction comme MOVE (A1), D1 lit l'octet situé à l'adresse stockée dans A1 et le place dans D1, sans utiliser de second octet significatif pour l'opérande.

Exemple : comparaison Python / Assembleur LM0

Traduire une structure conditionnelle simple éclaire la correspondance entre logique haut niveau et séquences d'instructions. Exemple Python :

if x > 0:

y = 1

else:

y = 0

Exemple conceptuel en pseudo-assembleur LM0 (illustratif) :

; charger x en D0

MOVE x_addr, D0

; comparer D0 à 0

SUB #0, D0

; si négatif ou nul -> saut vers label_else

JLE label_else

; y = 1

MOVE #1, y_addr

JMP label_end

label_else:

MOVE #0, y_addr

label_end:

Ce schéma montre la correspondance mnémonique et permet d'identifier les points d'optimisation (réduction des sauts, utilisation des flags du SR) lors du passage au code machine.