Bus et mémoires : notions clés. Document décrivant l'organisation des voies de communication (bus) et les technologies de mémoire (ROM, RAM, SDRAM, DDR, RDRAM) employées sur les plates‑formes PC. Présentation des échanges entre processeur, chipset et périphériques, des conséquences sur la latence et la topologie de la carte mère. Cliquez sur le bouton de téléchargement pour obtenir le guide complet au format PDF.

🎯 Ce que vous allez apprendre

- Rôle et architecture du chipset (Northbridge (Pont Nord) / Southbridge (Pont Sud)) — identification des fonctions respectives du Northbridge et du Southbridge et compréhension de leur liaison par le bus interne. Explications sur la migration du contrôleur mémoire vers le processeur et ses effets sur la latence et la topologie de la carte mère.

- Topologie des bus et Front Side Bus (FSB) — décryptage des canaux de communication (bus d'adresse, bus de données, bus de contrôle) et du rôle du FSB dans l'accès à la mémoire. Analyse des impacts de la fréquence du bus et des wait states sur le débit effectif entre CPU and mémoire.

- Familles de mémoires ROM et Flash — distinction entre ROM, PROM, EEPROM et Flash EPROM, usages sur la carte mère (BIOS, configuration) et critères de choix selon fréquence de reprogrammation et fiabilité.

- Évolution des RAM : DRAM, SDRAM, RDRAM, DDR — principes de rafraîchissement, synchronisation et double transfert (DDR) avec impacts sur la bande passante ; comparaison des débits théoriques (PC1600, PC3200, PC800 RDR) et évaluation pratique selon l'architecture de la carte mère.

- Mode double canal et UMA — mécanisme et conditions d'activation du dual‑channel, influence de l'Unified Memory Architecture sur les performances graphiques et critères pour mesurer l'amélioration réelle du débit mémoire.

- Compatibilité chipset‑mémoire et critères de sélection — lecture des contraintes de compatibilité entre familles de processeurs et chipsets, influence des interfaces intégrées (USB, SATA, PCI‑Express) et anticipation des limitations de performance.

- Mémoire cache et SRAM — rôle de la mémoire statique (SRAM) et de la mémoire CMOS dans la conservation des paramètres du BIOS.

- Standards et contrôleurs d'extension — analyse des contrôleurs de bus et arbitrage pour évaluer la compatibilité matérielle des machines mobiles (PCMCIA, CardBus, ExpressCard).

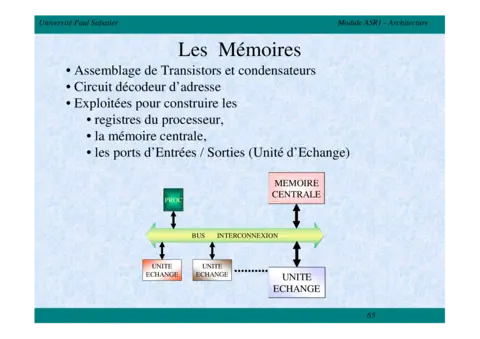

Les trois types de bus système

- Bus d'adresse (sélection de l'emplacement)

- Bus de données (transfert des informations)

- Bus de contrôle (signaux de synchronisation)

La capacité d'adressage du processeur est déterminée par la largeur du bus d'adresse (2n, où n est le nombre de lignes).

Architecture des bus d'extension et communication CPU

Organisation fonctionnelle entre processeur, contrôleur de bus et interfaces d'extension : description de l'arbitrage des transactions, de la sérialisation des accès et de l'interaction entre les différents niveaux de mémoire (cache, SRAM et mémoire principale). Impact des ponts logiques et des adaptateurs d'extension sur la latence et règles pratiques pour minimiser les goulets d'étranglement lors de l'ajout de périphériques sur des plateformes mobiles.

- Arbitrage du bus — mécanisme permettant de gérer les conflits lorsque plusieurs périphériques (Bus Masters) tentent d'accéder simultanément au bus.

Calcul et limites de l'adressage mémoire

L'espace adressable dépend directement du nombre de lignes d'adresse : l'adressage maximal théorique en octets est égal à 2n, où n représente les lignes d'adresse. Par exemple, un processeur 32 bits dispose d'un espace adressable théorique de 232 octets (≈4 GiB). En pratique, l'espace utilisable peut être réduit par la réservation d'adresses pour mémoire-mappée (contrôleurs, BIOS) ou par limitations du chipset. Les cycles de bus et la largeur du bus d'adresse influencent la granularité et la latence des accès mémoire.

Le rôle des ponts (Bridges) dans l'architecture système

Les Northbridge (Pont Nord) et Southbridge (Pont Sud) jouent le rôle de ponts entre bus de fréquences et de protocoles différents : traduction de signaux, arbitrage des accès et isolation des domaines temporels. Le Northbridge assure historiquement la liaison haute‑performance (CPU ↔ mémoire, GPU), tandis que le Southbridge centralise les E/S lentes (USB, SATA, PCI). La migration du contrôleur mémoire vers le processeur réduit la charge du Northbridge mais renforce l'importance des bridges pour gérer les interfaces périphériques.

Le décodage d'adresses et la sélection de boîtiers

Le décodage d'adresses utilise les lignes d'adresse (A0…An) pour identifier la zone mémoire ou le périphérique ciblé. Un décodeur matériel (gate logic, PLA ou contrôleur intégré) examine les bits de poids fort et de poids faible afin d'activer une ligne de sélection (chip select). La sélection peut être simple (comparaison d'une plage par masque) ou hiérarchique (décodage multiple pour mapper ROM, RAM et registres d'E/S). En pratique, la conception réserve des plages contiguës avec un masque d'adressage ; un périphérique répond lorsque l'adresse bus correspond au range défini. Le découpage des plages impacte la facilité d'adressage et la répartition des interruptions ou ressources mémoire mappées.

Cycles de lecture et d'écriture sur le bus système

Une transaction entre CPU and RAM se déroule en phases : phase d'adresse (le processeur place l'adresse sur le bus), phase de commande (read/write, signaux de contrôle), phase de transfert de données et phase d'acquittement. Des signaux supplémentaires (par ex. wait, ready) permettent d'insérer des wait states lorsque la mémoire ou un périphérique met plus de temps à répondre. Lors d'une lecture, le contrôleur place l'adresse puis attend la diffusion de la donnée ; lors d'une écriture, la donnée est mise sur le bus by le master après l'adresse. L'arbitrage intervient si plusieurs masters demandent l'accès ; le bus grant signale l'accès accordé. L'optimisation des timings (setup, hold, cycles d'horloge) réduit la latence effective et augmente le débit utile.

Exemple concret de largeur de bus : sur un bus de données 16 bits, deux caractères ASCII (2 × 8 bits) peuvent être transférés dans un seul mot de 16 bits, réduisant le nombre de cycles nécessaires pour envoyer une paire de caractères. Cet exemple illustre l'importance de la largeur du bus sur le nombre de cycles requis pour un transfert donné.

📑 Sommaire du document

💡 Pourquoi choisir ce cours ?

Document technique combinant descriptions conceptuelles et tableaux chiffrés de fréquences et de bandes passantes pour des comparaisons pratiques. Perspective historique et opérationnelle avec exemples de plateformes (Intel X58, Z77) et conseils de compatibilité chipset‑mémoire. Contenu structuré selon une méthodologie technique et des références aux spécifications industrielles (JEDEC, PCI‑SIG), accompagné de tableaux comparatifs pour faciliter la décision d'achat ou d'assemblage. Rédigé by Chris Hard, contributeur technique, avec un focus pratique sur le choix de la carte mère et l'optimisation du débit mémoire.

👤 À qui s'adresse ce cours ?

- Public cible : techniciens matériels, étudiants en architecture des systèmes et assembleurs de PC souhaitant comprendre les interactions chipset/mémoire pour optimiser performances et compatibilité.

- Prérequis : notions d'architecture PC (processeur, carte mère, périphériques), compréhension des unités de fréquence et de bande passante (MHz, MB/s) et capacité à lire des spécifications techniques.

❓ Foire Aux Questions (FAQ)

Quelle est la différence fonctionnelle entre Northbridge et Southbridge ? Le Northbridge gère les échanges à haute vitesse entre CPU, mémoire centrale et souvent la carte graphique (contrôleur mémoire, PCI‑Express), tandis que le Southbridge prend en charge les E/S lentes (USB, SATA, ports d'extension). Les deux communiquent via un bus interne au chipset ; la migration du contrôleur mémoire vers le CPU réduit les allers‑retours et peut diminuer la latence.

En quoi le mode double canal améliore‑t‑il les performances mémoire ? Le double canal permet au contrôleur mémoire d'accéder simultanément à deux modules identiques, doublant théoriquement la bande passante disponible. L'amélioration effective dépend du chipset, de la charge applicative et de la symétrie des modules ; sans barrettes strictement identiques l'avantage peut être nul.